The CPU processes an instruction, then the DMA controller transfers one information value, and so forth. Data just isn’t transferred as shortly, however CPU is not https://www.xcritical.com/ idled for as lengthy as in burst mode. Cycle stealing mode is beneficial for controllers that monitor knowledge in actual time.

Where a peripheral can turn out to be a bus grasp, it can instantly write to system memory with out the involvement of the CPU, offering reminiscence handle and control signals as required. Some measures must be offered to put the processor right into a hold situation in order that bus contention doesn’t occur. In summary, DMA is a crucial function for modern embedded methods that handle an abundance of sensors and require high throughput, efficiency, and low energy operation. It behaves like a coprocessor devoted completely to reminiscence and peripheral bus transactions. Burst DMA occurs via infrequent giant bursts, where the DMA controller sends as much data to the vacation spot buffer as the buffer can hold.

Advantages Of Dma Controller

DMA controller needs the same old circuits of an interface to speak with the CPU and Input/Output devices. Imagine a CPU outfitted with a cache and an external memory that might be accessed instantly by devices utilizing DMA. When the CPU accesses location X in the reminiscence, the present value will be saved within the cache. Subsequent operations on X will update the cached copy of X, but not the external memory version of X, assuming a write-back cache. If the cache just isn’t flushed to the memory earlier than the subsequent time a device tries to access X, the gadget will obtain a stale worth of X. “The console” (or other computer) is made up of varied elements, including the processor, the memory, and peripherals similar to video display controllers, I/O chips to read from a keyboard or joystick, disk controllers, and so on.

System assets such as the CPU, reminiscence, hooked up I/O devices and a DMA controller are related through a bus line, which can be used for DMA channels. The DMA controller is used to start reminiscence read/write cycles and to generate reminiscence addresses. Using DMA is crucial for so much of functions to minimize direct market access forex power consumption and lighten processor masses. For instance, well being and wearable units deal with massive amounts of data throughput, however they also must conserve as much battery charge as potential, all while dealing with delicate data.

Otherwise, the working system would want to work around the issue by either using expensive double buffers (DOS/Windows nomenclature) also called bounce buffers (FreeBSD/Linux), or it could use an IOMMU to provide handle translation services if one is present. These symbols, seen on hardware schematics of computer systems with DMA functionality, symbolize digital signaling lines between the CPU and DMA controller. A gadget that makes use of DMA must be configured to make use of both traces of the assigned DMA channel. DMA can be used for “reminiscence to reminiscence” copying or transferring of knowledge inside memory. DMA can offload expensive reminiscence operations, such as giant copies or scatter-gather operations, from the CPU to a devoted DMA engine. DMA is of curiosity in network-on-chip and in-memory computing architectures.

Not The Answer You’re Looking For? Browse Other Questions Tagged Hardwareprocessordma Or Ask Your Own Query

The microprocessor, or central processing unit (CPU), is freed from involvement with the information transfer, speeding up total laptop operation. As an example usage of DMA in a multiprocessor-system-on-chip, IBM/Sony/Toshiba’s Cell processor incorporates a DMA engine for every of its 9 processing components including one Power processor factor (PPE) and eight synergistic processor components (SPEs). Since the SPE’s load/store instructions can read/write solely its personal local memory, an SPE totally depends on DMAs to switch knowledge to and from the primary reminiscence and native memories of other SPEs. Thus the DMA acts as a primary means of knowledge transfer among cores inside this CPU (in distinction to cache-coherent CMP architectures such as Intel’s cancelled general-purpose GPU, Larrabee).

The CPU then commands the peripheral gadget to initiate an information transfer. The DMA controller then provides addresses and read/write management strains to the system memory. Each time a byte of data is prepared to be transferred between the peripheral gadget and reminiscence, the DMA controller increments its inside handle register till the total block of data is transferred. The cycle stealing mode is utilized in systems by which the CPU shouldn’t be disabled for the length of time wanted for burst switch modes. In the cycle stealing mode, the DMA controller obtains access to the system bus the identical method as in burst mode, using BR (Bus Request) and BG (Bus Grant) alerts, which are the two alerts controlling the interface between the CPU and the DMA controller. However, in cycle stealing mode, after one unit of information transfer, the control of the system bus is deasserted to the CPU by way of BG.

Like domestically based mostly DMA transactions, RDMA frees up sources and improves throughput and performance. This leads to faster data transfer rates and decrease latency between RDMA-enabled methods. In burst mode, a whole block of knowledge is transferred in a single contiguous sequence. Once the DMA controller is granted entry to the system bus by the CPU, it transfers all bytes of knowledge within the information block earlier than releasing control of the system buses again to the CPU, but renders the CPU inactive for relatively long periods of time. To perform input, output, or memory-to-memory operations, the host processor initializes the DMA controller with the variety of words to switch and the reminiscence handle to make use of. Direct Memory Access (DMA) is a functionality provided by some laptop bus architectures that enables information to be sent directly from an attached device, such as a disk drive, to the main memory on the pc’s motherboard.

When BG (bus grant) input is zero, the CPU can communicate with DMA registers. When BG (bus grant) input is 1, the CPU has relinquished the buses and DMA can talk immediately with the memory. Usually, a specified portion of memory is designated as an area for use for direct memory access. For example, within the Industry Standard Architecture bus standard, as a lot as sixteen MB of memory can be addressed for DMA. Other bus requirements may allow access to the total range of memory addresses. Peripheral element interconnect makes use of a bus master with the CPU delegating I/O management to the PCI controller.

Modes Of Operation

This may give a definite benefit in purposes that require extended battery life, similar to wearable sensor hubs and smart watches. As originally defined, DMA controllers relied on the fact that the bus had separate strains to assert for memory read/write, and I/O read/write. The DMA controller took advantage of that by asserting each a memory read and I/O write (or vice versa) at the identical time. The DMA controller then generated successive addresses on the bus, and information was learn from reminiscence and written to an output port (or vice versa) each bus cycle.

Spotify, Epic Games, and Others Argue Apple’s App Store Changes Do Not Comply With DMA – MacRumors

Spotify, Epic Games, and Others Argue Apple’s App Store Changes Do Not Comply With DMA.

Posted: Fri, 01 Mar 2024 08:00:00 GMT [source]

For example, RDMA is beneficial when analyzing massive data, in supercomputing environments and for machine learning that requires low latencies and excessive switch charges. Scatter-gather or vectored I/O DMA permits the transfer of information to and from multiple reminiscence areas in a single DMA transaction. It is equivalent to the chaining together of multiple easy DMA requests.

Direct Reminiscence Access Dma – How Does It Work?

For instance, when managing an ADC that’s continuously sending data, a processor may be interrupted so often that it struggles to accomplish other tasks. DMA is a technique of moving information and minimizing processor involvement in large or quick knowledge transactions. You can think of the DMA controller as a coprocessor whose sole objective is to work together with reminiscence and peripherals. This permits the primary processor to successfully manage a greedy peripheral, focus on another task, and even fall asleep and preserve energy while information transactions happen within the background. For example, on Arm® architectures, a DMA module can operate throughout LP2 (sleep) or LP3 (run) modes.

The higher path corresponds to knowledge move, and the decrease path represents control/status move between the advanced high efficiency bus (AHB) and the DMA logic. The DMA controller can behave as a buffer interface between the AHB and reminiscence or peripheral modules, depending on how it is configured. DMA logic sits between the DMA buffer and each peripheral to independently manage every unique peripheral bus throughout transactions. A DMA operation can transfer up to 32 bytes at a time, provided the source/destination buffers can contain this much data. The buffer can hold as much as 16 MB and is configurable to transmit or receive I2C, SPI, I2S, and UART in addition to internal reminiscence transfers.

Pci

The motivation is to off-load multiple input/output interrupt and information copy duties from the CPU. Brandon Hurst is a field functions engineer focusing on software program and embedded systems. His primary expertise is in embedded systems, as properly as battery charging and gas gauging. He graduated with a bachelor’s degree in electrical engineering from Cal Poly, San Luis Obispo and joined Maxim Integrated (now part of Analog Devices) in January 2021. 8257 DMA Controller is a sort of DMA Controller, that when a single Intel 8212 I/O device is paired with it, becomes four channel DMA Controller. It accommodates two 16-bit registers, one is DMA Address Register and the other one is Terminal Count Register.

With DMA, a CPU initiates a knowledge transfer with an attached gadget and may still carry out other operations while the information switch is in progress. DMA permits a pc to transfer data to and from units with less CPU overhead. Instead, A PCI system can request management of the bus (“turn out to be the bus master”) and request to read from and write to system memory. More exactly, a PCI component requests bus possession from the PCI bus controller (usually PCI host bridge, and PCI to PCI bridge[6]), which is able to arbitrate if several gadgets request bus possession concurrently, since there can solely be one bus master at one time. When the element is granted ownership, it’s going to problem normal learn and write commands on the PCI bus, which will be claimed by the PCI bus controller. In a bus mastering system, also identified as a first-party DMA system, the CPU and peripherals can every be granted control of the reminiscence bus.

Enterprise Economics

Without DMA, when the CPU is using programmed input/output, it is typically totally occupied for the entire duration of the learn or write operation, and is thus unavailable to perform other work. With DMA, the CPU first initiates the switch, then it does different operations whereas the switch is in progress, and it lastly receives an interrupt from the DMA controller (DMAC) when the operation is done. This feature is beneficial at any time that the CPU can not keep up with the rate of knowledge transfer, or when the CPU needs to perform work whereas waiting for a relatively slow I/O information transfer.

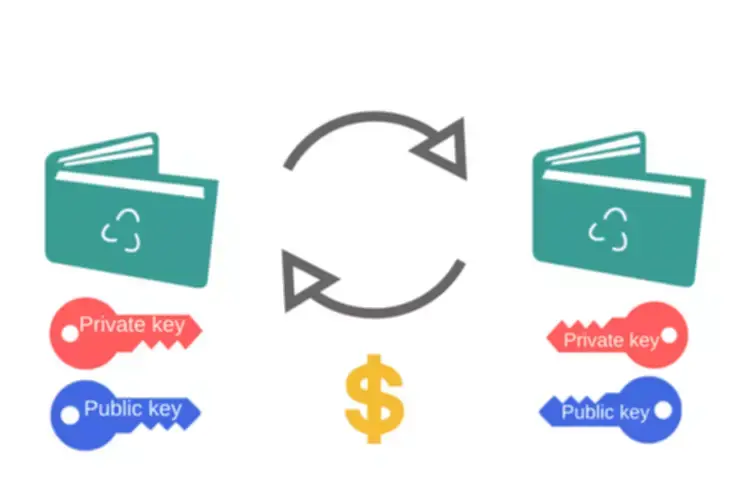

When utilizing “programmed I/O,” the CPU reads data from or writes information to a peripheral and, if the information have to be stored in memory, the CPU does that as well. So the CPU might read a byte from the disk controller, retailer that byte into a buffer in reminiscence, and repeat that to learn a complete sector from disk. You can undertake the RDMA know-how to enable computer systems in a network to trade data in the primary reminiscence without involving the processor, cache or operating system of both computer. But you can also use the DMA characteristic to instantly send data from an connected gadget to the memory on the computer’s motherboard. An various to DMA is Ultra DMA, which provides a burst knowledge transfer rate up to 33 megabytes per second (MBps). Hard drives which have Ultra DMA/33 additionally support programmed input/output (PIO) modes 1, 3 and 4, and multiword DMA mode 2 at 16.6 MBps.